Leporisとは?

Leporis(レポリス)は、超伝導単一磁束量子(SFQ)集積回路の測定結果を効率的に管理し、共有するための、オンラインデータベースシステムです。

Leporis誕生の背景と目的

超伝導デバイスを用いた単一磁束量子(SFQ)に基づく集積回路は、数十GHzから100GHz以上へ及ぶ極めて高速な論理回路を、半導体の1/1000またはそれ以下の消費電力で実現することができるため、次世代の大規模集積回路(LSI)技術として、1990年代以降アメリカ、日本、ヨーロッパを中心に盛んに研究が行われてきました。

NEC社が開発し、国際超電導産業技術研究センター(ISTEC)での研究開発を経て、産業技術総合研究所(AIST)が提供している「標準プロセス [1]」は、超伝導体としてニオブを用いた、世界でもっとも信頼性の高い超伝導LSI製造ラインです。標準プロセスを発展させ、さらなる高速化・高密度化を狙った「アドバンストプロセス [2]」の開発も進み、マイクロプロセッサをはじめとする複雑で大規模な超伝導LSIが動作実証に成功しています。

SFQ集積回路の例: (左)世界で初めて動作したSFQマイクロプロセッサプロトタイプ [3]。4999接合を集積し、15GHzでの動作実証に成功。設計は名古屋大と横浜国立大。(右)メモリを搭載し、プログラム内蔵式の計算が可能なマイクロプロセッサ [4]。10,603接合を集積し、50GHzでの動作実証に成功。設計は名古屋大と京都大。

しかしながら、SFQ回路は磁束量子という大変小さな物理量ひとつひとつを信号として扱っており、しかもその高速性を活かすためにピコ秒(一兆分の一秒)単位の精度でSFQ信号を制御する必要があります。そのため、ノイズや作製ばらつきに影響されやすく、大規模なSFQ集積回路を動作させるための技術開発は容易ではありません。NEC、名古屋大学、通信総合研究所(現 情報通信研究機構)、横浜国立大学は、産官学連携によりCONNECTセルライブラリと一連の設計ツールを開発し、標準プロセスを利用した超伝導LSI技術の基盤を築きました。その後、ISTECへ移った試作担当者も含めた拡大全体会議を重ね、アドバンストプロセスの開発では、名古屋大学・横浜国立大学の設計者と試作担当者が綿密に連携して、デバイス構造の決定から設計手法の確立までを成し遂げています。

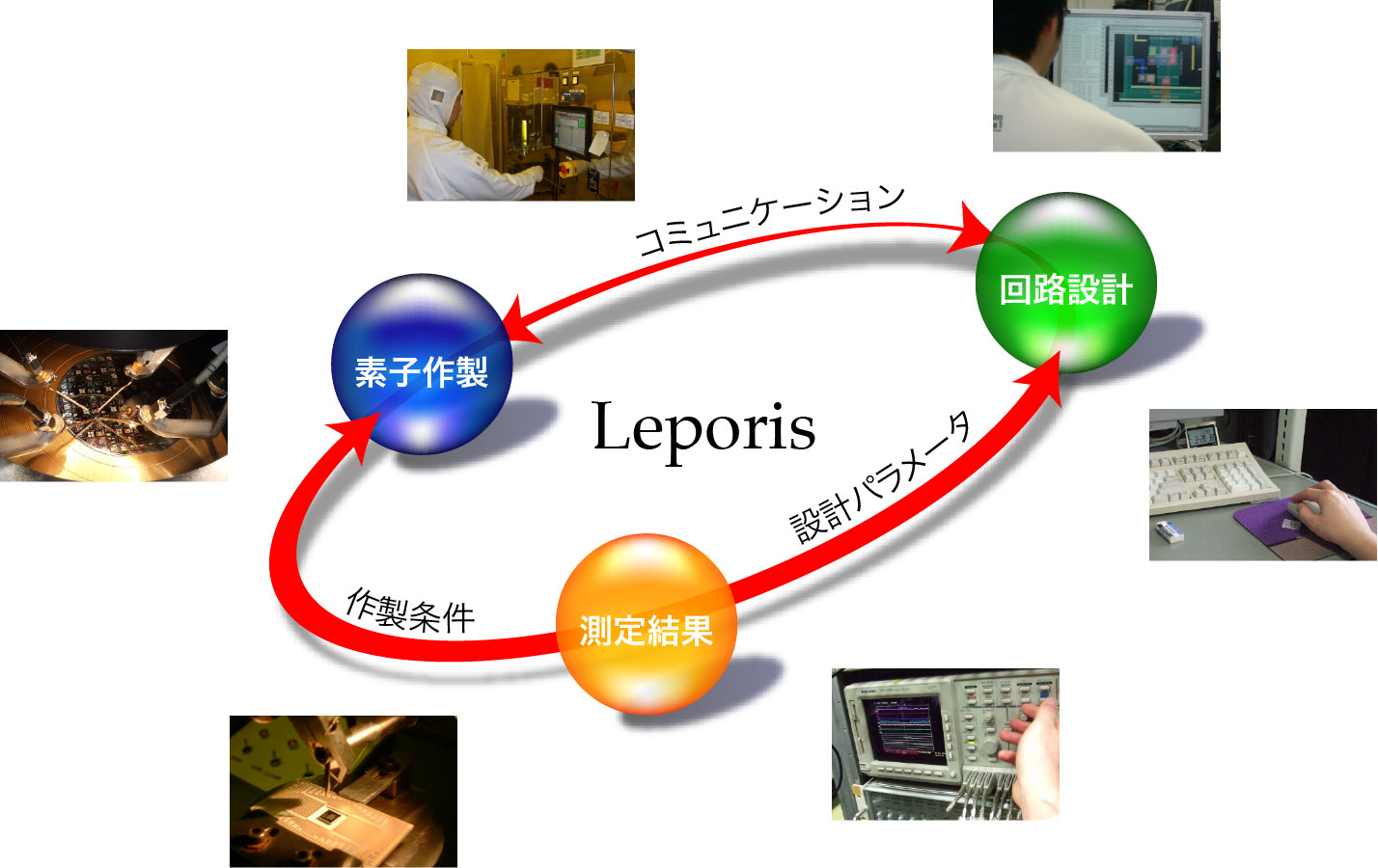

集積回路技術の研究では、素子作製技術と回路設計技術の両面から研究を進めることが必要です。大規模化や信頼性の進展には、試作したLSIチップの評価結果に基づいた、作製プロセスや回路設計手法の継続的な改善が欠かせません。Leporisは、さまざまな研究機関で評価されたLSIチップの測定結果をデータベースとして管理し、オンラインで共有することを目的とし、2006年9月より名古屋大学大学院量子工学専攻(当時)藤巻研究室で運用が開始されました。2009年12月、2014年12月、2017年3月には、日本学術振興会科学研究費補助金の助成(21760256、24760276、16H02796)を受けてシステムが強化され、現在も藤巻研究室で運用されています。

当初、LeporisへはISTEC、名古屋大学、横浜国立大学、情報通信研究機構が参加していましたが、2008年度より標準プロセスに携わる大学も加わっています。およそ60人以上の研究者(学生を含む)が利用しています。

Leporisの概要

Leporisでは、作製条件や物理的・電気的特性といった試作されたデバイス(素子)に関する情報、回路の集積規模や設計周波数といった回路設計データ、及び試作されたLSIチップで回路が期待通りに動作したかといった測定結果をデータベースにまとめています。

このデータベースから作製条件や設計パラメータと測定結果の関連を解析し、LSIチップの評価結果を効果的にフィードバックすることを目指します。また、Leporisはデバイス作製者と回路設計者で課題を共有する場としての役割も担います。データベースはオンラインで管理されており、試作に関わっている研究者であれば、いつでもどこからでもインターネットを通じてアクセスできます。

参考文献

- S. Nagasawa, Y. Hashimoto, H. Numata, and S. Tahara, “A 380 ps, 9.5 mW Josephson 4-Kbit RAM operated at a high bit yield,” IEEE Trans. Appil. Supercond., vol. 5, no. 2, pp. 2447–2452, Jun. 1995. DOI: 10.1109/77.403086

- S. Nagasawa et al., “Nb 9-layer fabrication process for superconducting large-scale SFQ circuits and its process evaluation,” IEICE Trans. Electron., vol. E97–C, no. 3, pp. 132–140, Mar. 2014. DOI: 10.1587/transele.E97.C.132

- M. Tanaka et al., “A single-flux-quantum logic prototype microprocessor,” 2004 IEEE International Solid-State Circuits Conference, pp. 298–529, Feb. 2004. DOI: 10.1109/ISSCC.2004.1332714

- R. Sato et al., “High-speed operation of random-access-memory-embedded microprocessor with minimal instruction set architecture based on rapid single-flux-quantum logic,” IEEE Trans. Appil. Supercond., vol. 27, no. 4, art no. 1300505, Jun. 2017. DOI: 10.1109/TASC.2016.2642049