単一磁束量子(SFQ)回路とは?

単一磁束量子(SFQ)回路は、これまでの半導体とは異なる超伝導体を利用し、従来技術では実現が困難な超高速・超低消費電力の演算処理を実現できる次世代ディジタル回路技術です。ここでは、SFQ回路の原理と特長を簡単に説明します。

動作原理

磁束は超伝導体を横切ることはできませんが、超伝導体でリングを作るとリングの穴の部分を通ることはできます。しかし、この穴を通ることができる磁束の量は飛び飛びの値しかとれず、その最小単位を磁束量子と呼んでいます。単一磁束量子(SFQ: single flux quantum)回路は、超伝導リング内に磁束が1本あるかないかを「1」、「0」に対応させて演算を行います。このアイディアは、1976年に東北大学の中島らにより提案され [1, 2]、その後、モスクワ州立大学のリカレフらによる体系化を経て [3]、現在の形に至っています。

リング内の磁束量子を操作するには、ジョセフソン接合をリングに挿入します。これは、ごく薄い絶縁膜を超伝導体の間に挟んで弱く結合させた構造をしています。ジョセフソン接合には抵抗ゼロで電流が流れますが、臨界電流値と呼ばれる一定電流量以上の電流が流れるとスイッチし、このとき磁束量子は絶縁膜を通り抜けてリングに出入りすることができます。

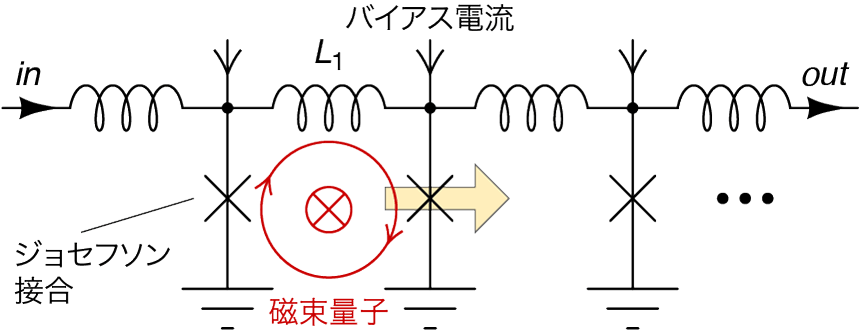

下の図1にSFQ回路の基本動作原理を示します。×印はジョセフソン接合であり、超伝導体の部分はインダクタ(コイル)として表されます。この回路はジョセフソン伝送路(JTL: Josephson transmission line)と呼ばれ、超伝導リングを数珠繋ぎにし、電源となる直流バイアス電流を加えたものです。磁束量子がリング内に入ると、リングに周回電流が発生します。インダクタンスL1を小さく設計しておくと、バイアス電流と周回電流の和によりジョセフソン接合がスイッチし、磁束量子は隣のリングに移ります。これを繰り返し、JTLは磁束量子を順次伝搬させる機能を持ちます。

図1 ジョセフソン伝送路(JTL)

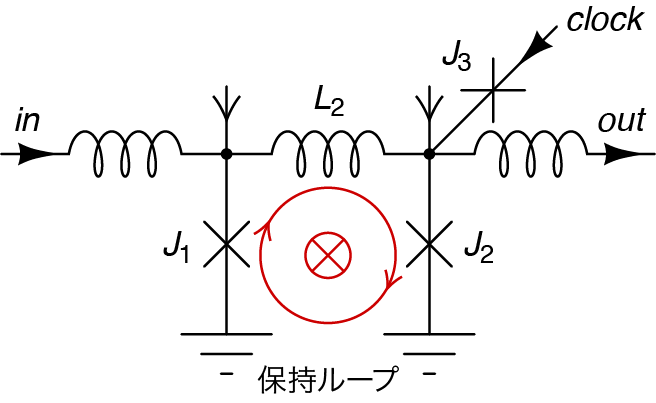

図2はもう少し複雑な例で、データを一時的に蓄えるDフリップフロップです。インダクタンスL2を大きな値に設定しておくと、周回電流が流れてもジョセフソン接合J2がスイッチせず、リングにSFQを留まらせることができます。ここに別のclock端子からクロック信号となる磁束量子が来ると、さらにその周回電流が加わり、J2がスイッチして保持されていた磁束量子がリングの外に飛び出ます。J3の臨界電流値はJ2よりも少し小さく設定しておきます。磁束が保持されていないときにclock端子から磁束量子が来た場合は、J2の代わりにJ3がスイッチすることで出力に磁束量子が現れないようにします。

図2 SFQ回路によるDフリップフロップ

SFQ回路では、信号の「0」と、磁束量子がまだ来ていない状態の区別をつけるための工夫が必要になります。通常のSFQ回路では、Dフリップフロップの例で示したように、基準となるクロック信号を利用し、2つのクロック信号間にデータ信号の入力があれば「1」、なければ「0」と定義しています。この定義に従うと、図2の回路はclock入力直前の値を保持する、Dフリップフロップとして働くことが分かります。

このように、リングのトポロジや回路パラメータを変えることにより磁束量子の分岐、合流、伝搬、保持が行え、相互作用により種々の論理演算が実現できます。また、クロック信号に対して待ち合わせが必要なことから、原理的に全てのSFQ論理ゲートは一時的にデータを保持する、ラッチ機能を持つことになります。

磁束量子を使った論理回路の実現方法は、他にもいくつか考えられますが、上記はリカレフらがまとめた、rapid single flux quantum(RSFQ)回路と呼ばれる基本的な方式になります。SFQ回路とRSFQ回路とはほぼ同義で使われることもありましたが、最近はRSFQ回路を発展させた、よりエネルギ効率の高い回路方式も複数登場しており、これらの派生形も含め、磁束量子を情報担体とするディジタル回路全般をSFQ回路と呼ぶことが一般的になっています。RSFQ回路に関するより詳しい解説は、参考文献 [3](英語)にあります。

特長

SFQ回路では、磁束量子がジョセフソン接合を横切る際にのみインパルス的に電圧が発生します。パルスの高さは数ミリボルト、幅は数ピコ秒です。

SFQ回路の特長は、全てこのインパルス状の信号に由来します。電圧レベルを信号とする従来の方式では、配線容量を充放電する必要がありますが、SFQ回路ではその必要はありません。このことは、一本の配線上に複数のパルス信号を載せることが可能であることを意味します。

信号の伝搬に超伝導体による受動線路(PTL: passive transmission line)が利用できるのもSFQ回路の大きな特長です。超伝導PTLはほぼ無損失・無分散のため、パルス信号は光速と同程度の速度で弾道的に伝搬します。従って、チップ内・チップ間にかかわらず100GHz以上の高スループットでの信号伝送が可能です。また、SFQ回路の電力消費はジョセフソン接合がスイッチする瞬間にのみ起こるため、本質的に必要なゲート当たりの消費電力は半導体デバイスに比べて3桁以上小さく、高集積化を進めても発熱の問題はありません。これらの特長から、SFQ回路はマルチチップモジュール(MCM)や三次元実装のような超高密度実装にも向いていると言え、これまでの半導体に代わる次世代の大規模集積回路(LSI: large scale integration)技術として期待されています。

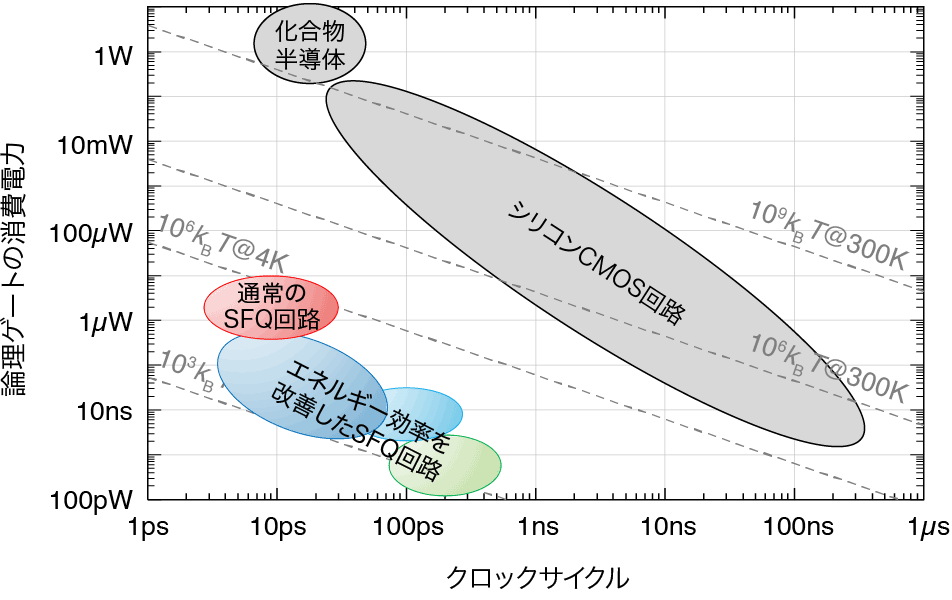

図3に代表的な論理ゲートである、Dフリップフロップ1つあたりの消費電力とディジタル回路のクロック信号の周期(クロックサイクル)を簡単に比較した図を示します。一般に、消費電力とクロックサイクルにはトレードオフがあり、設計要求に応じて適当な動作点が選択されますが、両者の積は消費電力遅延積(PDP: power-delay product)と呼ばれ、集積デバイスの性能を評価する指標となります。2010年前後から、より消費電力の小さな超伝導ディジタル回路の回路方式の探求が盛んになっており、図に示すように、エネルギー効率のさらに優れたSFQ回路の派生形が誕生しています [4]。

図3 論理ゲートの消費電力とクロックサイクルの比較

応用分野

高速性、低消費電力性を特長とするSFQ回路は、さまざまな分野への応用が期待されています。

現在、医療、遺伝子解析、環境、気象、物質、材料、物理、化学、建築、機械設計、集積回路設計などあらゆる分野で、計算機によるシミュレーションなしには研究・開発を進められない状況にあります。極めて大規模で高性能なコンピュータである、スーパーコンピュータはSFQ回路の究極の応用分野と言えます。また、爆発的に増え続ける情報を集約的に処理するデータセンタのエネルギ消費は大きな社会問題となっており、微細化の限界を迎えつつある半導体CMOS回路に代わり、持続的な情報化社会の進展には新しい集積回路技術の登場が強く望まれます。SFQ回路はその第一候補と言えます。

日本及び米国では、SFQ回路を用いたマイクロプロセッサ(コンピュータの計算を行う部分)の研究が進められ、実証では日本が先行する形で、15–50GHzでSFQマイクロプロセッサを動作させることに成功しています [5, 6, 7, 8]。

用語解説

- 半導体

- 金属のような電気を良く通す「導体」と、電気を通さない絶縁体の中間的な性質を示す物質。代表的な材料としてシリコンが挙げられる。電気伝導を担う、自由に動くことのできる電子が適度に存在し、電圧をかけることによってその流れを制御することができるため、さまざまな機能素子を作ることができる。現在のコンピュータの内部では、増幅機能を持つ「トランジスタ」をスイッチとして利用し、計算を行っている。

- 超伝導体

- 極低温まで冷却すると突然電気抵抗がゼロになる性質(超伝導)を示す物質。一部の金属や化合物が超伝導になることが知られており、現在のSFQ回路ではニオブという金属が主に使われている。電気抵抗がゼロになる以外にも、超伝導体の内部には磁気が入れず、外へ押し出されてしまうなど特異な現象が起きる。

- ディジタル回路

- データを数値化して処理する回路で、電圧の高低を二進値の「1」[0」に対応させて計算する方式が最も一般的です。計算や記憶、伝送が容易に行える特徴があり、コンピュータなど広く使われている。

- 磁束量子

- 超伝導体のリング内に入ることのできる磁束の最小単位。リングにはこの整数倍の大きさの磁束しか入らない(磁束の量子化)。大きさはΦ0 = h/2e = 2.07×10-15 Wb。

- ジョセフソン接合

- 超伝導回路におけるスイッチの役割をする素子。超伝導体の間にごく薄い絶縁膜(約1ナノメートル)を挟んで弱く結合させた構造になっている。抵抗ゼロで電流が流れるが、一定量以上を流すとスイッチし、このときだけSFQ信号を通過させることができる。

- Dフリップフロップ

- データを一時的に記憶する論理回路の一つで、クロック入力があったときの入力の値を保持する働きをする。

- クロック信号

- 回路動作のタイミングをとるために使われる、周期的な信号。例えばコンピュータでは、1クロックごとに一つ一つの決められた処理を進めている。

- 大規模集積回路(LSI)

- 非常に多数(数千個から数億個以上)の素子を数平方センチメートルの中に一つにまとめた電子部品。コンピュータの計算回路(マイクロプロセッサ)をはじめ、ほとんどすべての電子機器に使われており、小型化、高機能化に大きく貢献している。

参考文献

- K. Nakajima, Y. Onodera, and Y. Ogawa, “Logic design of Josephson network,” J. Appl. Phys, vol. 47, no. 4, pp. 1620–1627, Apr. 1976. DOI: 10.1063/1.322782

- K. Nakajima, H. Mizusawa, H. Sugahara, and Y. Sawada, “Phase mode Josephson computer system,” IEEE Trans. Appil. Supercond., vol. 1, no. 1, pp. 29–36, Mar. 1991. DOI: 10.1109/77.80746

- K. K. Likharev and V. K. Semenov, “RSFQ logic/memory family: a new Josephson-junction technology for sub-terahertz-clock-frequency digital systems,” IEEE Trans. Appil. Supercond., vol. 1, no. 1, pp. 3–28, Mar. 1991. DOI: 10.1109/77.80745

- O. A. Mukhanov, “Energy-Efficient Single Flux Quantum Technology,” IEEE Trans. Appil. Supercond., vol. 21, no. 3, pp. 760–769, Jun. 2011. DOI: 10.1109/TASC.2010.2096792

- M. Tanaka et al., “A single-flux-quantum logic prototype microprocessor,” 2004 IEEE International Solid-State Circuits Conference, pp. 298–529, Feb. 2004. DOI: 10.1109/ISSCC.2004.1332714

- Y. Yamanashi et al., “Design and Implementation of a Pipelined Bit-Serial SFQ Microprocessor, CORE1β,” IEEE Trans. Appil. Supercond., vol. 17, no. 2, pp. 474–477, Jun. 2007. DOI: 10.1109/TASC.2007.898606

- A. Fujimaki, M. Tanaka, T. Yamada, Y. Yamanashi, H. Park, and N. Yoshikawa, “Bit-Serial Single Flux Quantum Microprocessor CORE,” IEICE Trans. Electron., vol. E91–C, no. 3, pp. 342–349, Mar. 2008. DOI: 10.1093/ietele/e91-c.3.342

- R. Sato et al., “High-speed operation of random-access-memory-embedded microprocessor with minimal instruction set architecture based on rapid single-flux-quantum logic,” IEEE Trans. Appil. Supercond., vol. 27, no. 4, art no. 1300505, Jun. 2017. DOI: 10.1109/TASC.2016.2642049